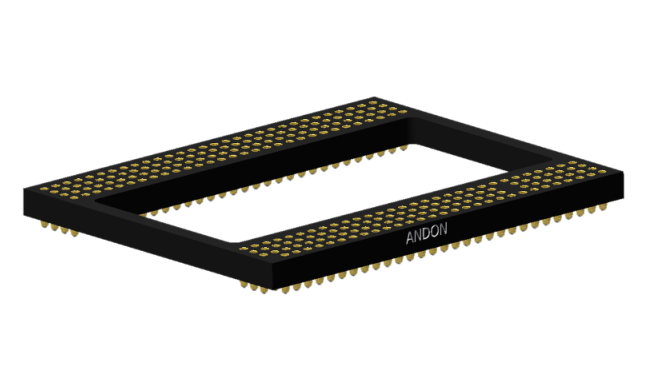

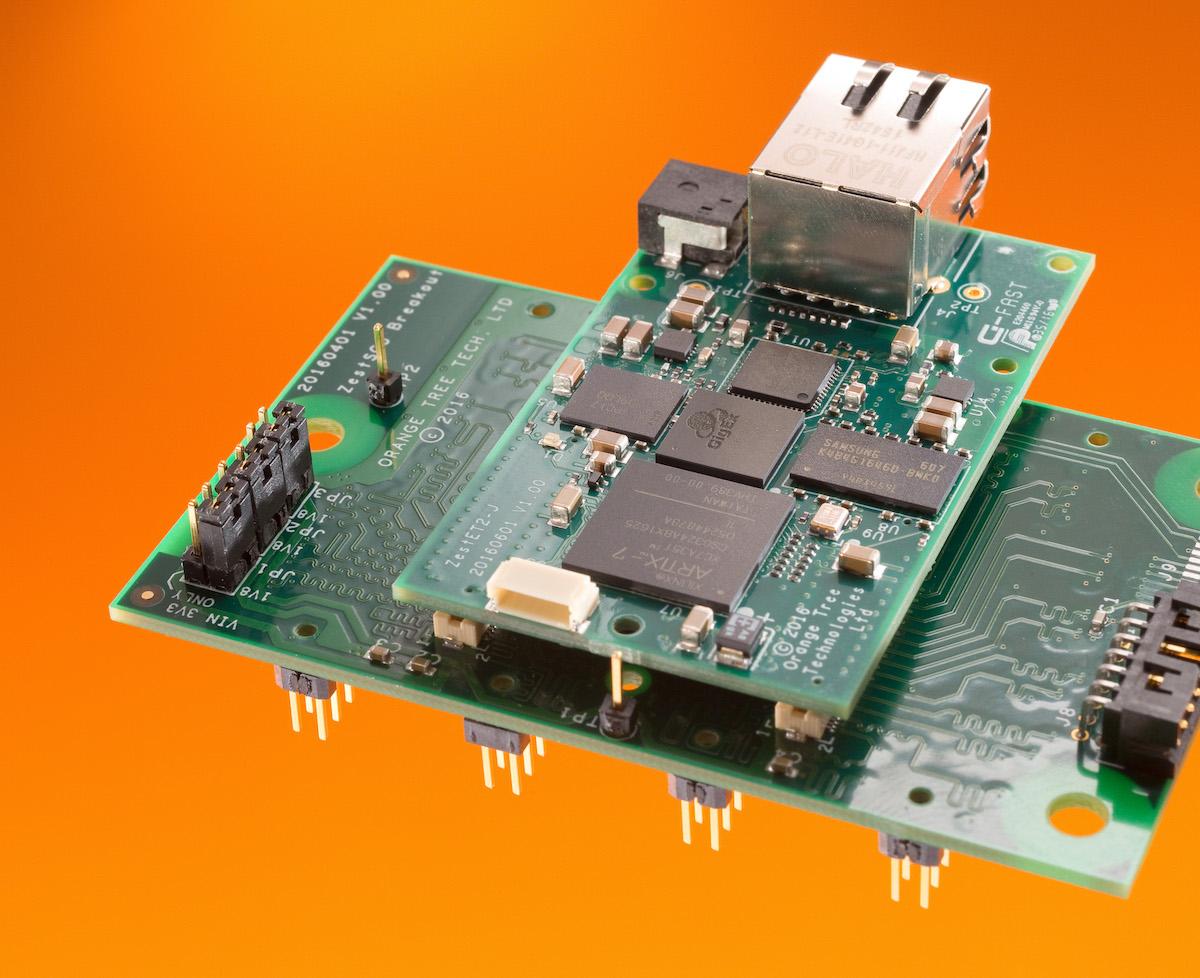

ZestET2-NJ Ethernet FPGA Module

The ZestET2-NJ是一款简单易用的 FPGA 板,它采用 Xilinx Artix-7可编程FPGA 已一个性能非常高的 TCP/IP 减负引擎 (TOE) 芯片., 用于数据流高速处理以及数据采集和控制。

Compared with ZestET2-J, ZestET2-NJ does not include the Ethernet jack or power jack to minimise the overall height of the final solution including carrier board and to allow flexible positioning of the connectors in the user's enclosure.

It provides a simple bridge between a high speed computer network and a programmable digital interface. The TOE sustains a data rate over 100MBytes/s in each direction and includes a user programmable CPU for optional higher level protocols.

Orange Tree's proprietary GigExpedite chip "GigEx" is a TOE that handles all the Ethernet communicati*** protocols. This le***es the Artix-7 FPGA completely free for the user's application, and means the user does not require any knowledge of Ethernet protocols. With the main processing engine implemented in TOE ha***are, sustained data rates over 100MBytes/sec are achieved.

The third generation of Orange Tree’s custom GigEx chip provides a user-programmable CPU. This is completely free for the user to program, for example with higher-level Ethernet protocols such as GigE Vision and Industrial Ethernet, or it can be left unprogrammed. You can read more about GigEx here.

With its compact form factor (40mm x 50mm), the module is ideally suited to integration in embedded systems and OEM equipment. It features a user programmable Xilinx Artix-7 FPGA, coupled with 512MBytes of high speed DDR3 memory. The FPGA can be programmed from on-board Flash, Ethernet or JTAG.

For evaluation there is a breakout board ***ailable. ZestET2-NJ-BRK connects the User FPGA IO pins to an FMC connector and a 0.1” pitch header. It includes all power supplies for the ZestET2-NJ and the FMC and is powered from 12V. It also has the standard Xilinx JTAG header for the ZestET2-NJ User FPGA and the FMC.

Benefits

-

Easy to use with no detailed networking knowledge required

-

Offers simple access to very fast data rates over Gigabit Ethernet without h***ing to integrate complex networking ha***are and software

-

Devices connected to User FPGA can communicate via Ethernet without using a processor or incurring processor overheads

-

Virtually no FPGA resources used for network communicati***, so most of FPGA ***ailable for data processing

-

Can be extended to application layer protocols running above TCP or UDP either in User CPU or User FPGA

Features

-

More than 100MBytes/sec sustained data rate in each direction over Gigabit Ethernet

-

Xilinx Artix-7 User FPGA and 512MBytes DDR3 memory

-

105 User IO pins

-

GigEx ha***are TOE for UDP and TCP/IP offload

-

User CPU within the GigEx TOE for user defined application layer protocols (or can be left unprogrammed)

-

Real-time Ethernet extensi*** Precision Time Protocol (PTP) and Synchronous Ethernet (SyncE)

-

Single power supply and low external component count

-

Free Windows tools based on GCC and Eclipse for the GigEx User CPU

-

Free tools ***ailable from Xilinx for creating FPGA designs (Webpack)

-

Windows and Linux software support for configuring and communicating with the User FPGA

-

Logic cores for all FPGA interfaces

-

Reference designs (including C, VHDL and Verilog source)

-

ZestDAQ framework of logic cores and host software for quick implementation of data acquisition and control applicati***